本笔记首先简述了由半导体物理推导出的MOS器件的电学特性,然后介绍了SiC 器件的工艺,以及一些例子中SiC CMOS的参数。

MOS器件特性

MOS器件I/V特性

阈值电压:定义为反型层浓度等于掺杂浓度,实际上在IV测量中很难直接测量。

其中,$|Q’{SD}(\max)|=eN_a x{dT}$ , 为反型层/空间电荷区的总电荷。

$x{dT}=\left(\frac{4\epsilon_s\phi{fp}}{eN_a}\right)^{1/2}$ 为空间电荷区最大宽度。

电势 $\phi_{fp}=V_t \ln(\frac{N_a}{n_i})$ 是掺杂带来的费米能级变化。$V_t=KT/e$是热电压。

三极管区:$VG>V{th}$ , 存在反型层,且反型层没有被夹断。沟道电压从0V变化到$V_{GS}$.

此时的$ID-V{DS}/V_{GS}$关系为:

可以看出$ID$ 与 $V{GS}$ 呈现出一次关系,与 $V{DS}$ 呈现出二次关系(在 $V{DS}$ 很小的时候可忽略二次项)。电流的极大值出现在 $V{DS}=V{GS}-V_{th}$.

三极管区峰值电流:$I{D,\max}$,与栅极电压 $V{GS}$ 成二次关系:

导通电阻:$R{on}$,当$V{DS} << 2(V{GS}-V{th})$ 很小的时候,$ID$ 与 $V{DS}$ 近似成线性关系,比值即为导通电阻。

饱和区:当MOS工作在 $V{DS}>V{GS}-V{th}$ 区域的时候,电流并不会按照抛物线减少,而是进入饱和区。原因就在于反型区的电荷密度是正值,栅压增大,沟道的反型层会被夹断,Q=0 的点将不断向源极移动。此时的有效沟道长度记为 $L’$ ,在此处电压等于 $V{GS}-V_{th}$.

此时的$ID-V{DS}/V_{GS}$关系为:

跨导:漏电流随栅极电压的变化率。饱和区的跨导为:

注意到饱和区跨导正好是导通电阻的倒数。

三极管区的跨导:

三极管区的跨导会减小,因此利用MOS器件的放大效应时,一般使器件工作在饱和区。

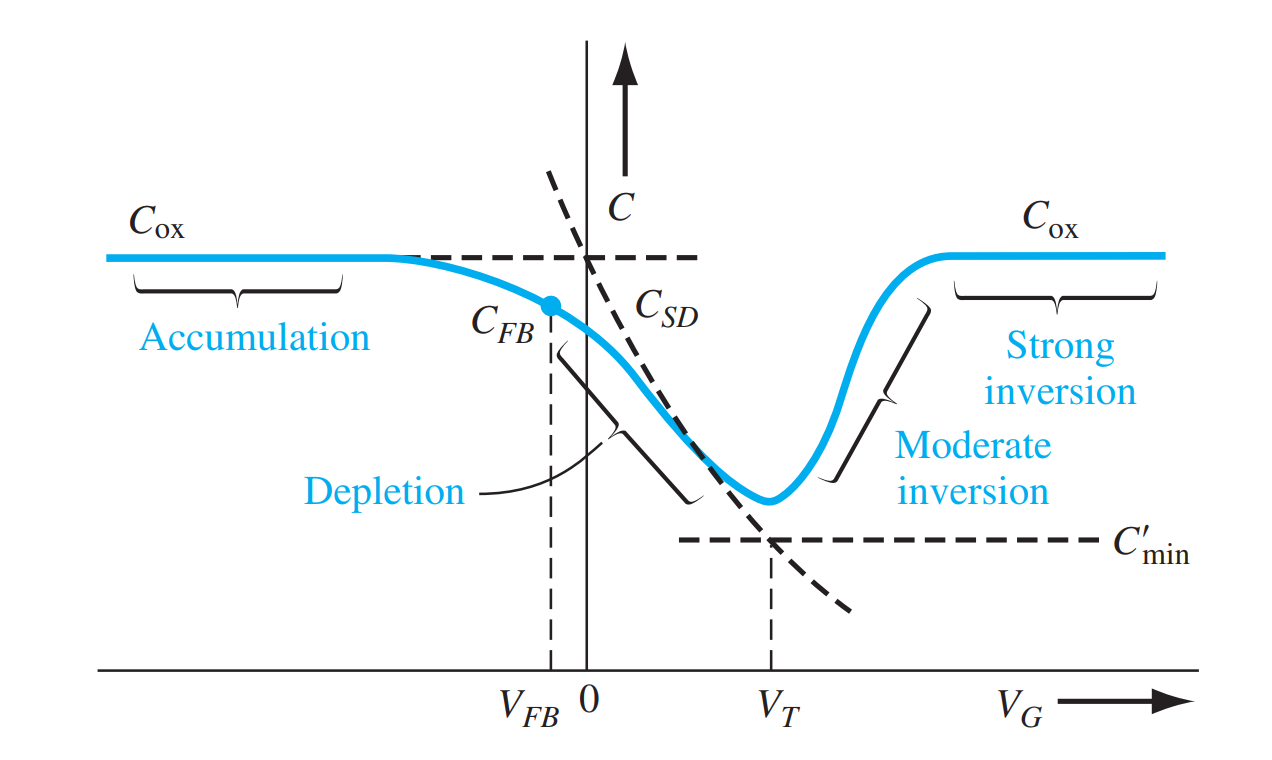

电容电压关系($C-V_{G}$特性):MOS电容有三种状态:堆积、耗尽和反型。

堆积区:对于pMOS,施加负的栅极电压时,界面会有空穴堆积。此时电容特性类似于平行板电容器。

耗尽区:pMOS施加一个微小正偏压,产生空间电荷区。电压改变将导致界面电荷的累积,以及空间电荷区的扩展。因此,电容等于两个电容串联:

总电容随着空间电荷区宽度的增加而减小。在空间电荷区宽度达到最大的时候,耗尽区电容达到最小。

反型区:在反型区,栅极电压进一步增大,界面的电荷密度增加,而空间电荷区的宽度不变。因此电容又回到和平行板电容器相同的情况。

平带电压 $V_{FB}$:在C-V曲线堆积区和耗尽区发生转换的地方,对应的栅极电压是平带电压。

固定氧化层电荷 $Q’_{ss}$:利用C-V曲线测出的平带电压和理想平带电压的差值就能确定等效固定氧化层电荷。

等效固定氧化层可以通过在栅极和沟道接触处进行小薄层注入来调控,注入应确保在阈值电压下完全耗尽。用这种手段可以调节平带电压,从而调节阈值电压。

界面电荷效应:可以由实验测到的C-V曲线的平滑度确定。界面处存在一系列在禁带中的能带,当栅极电压依次扫描堆积、耗尽和反型区域的时候,界面电荷由正变负(对于p掺杂衬底)。因此C-V曲线会变平滑。

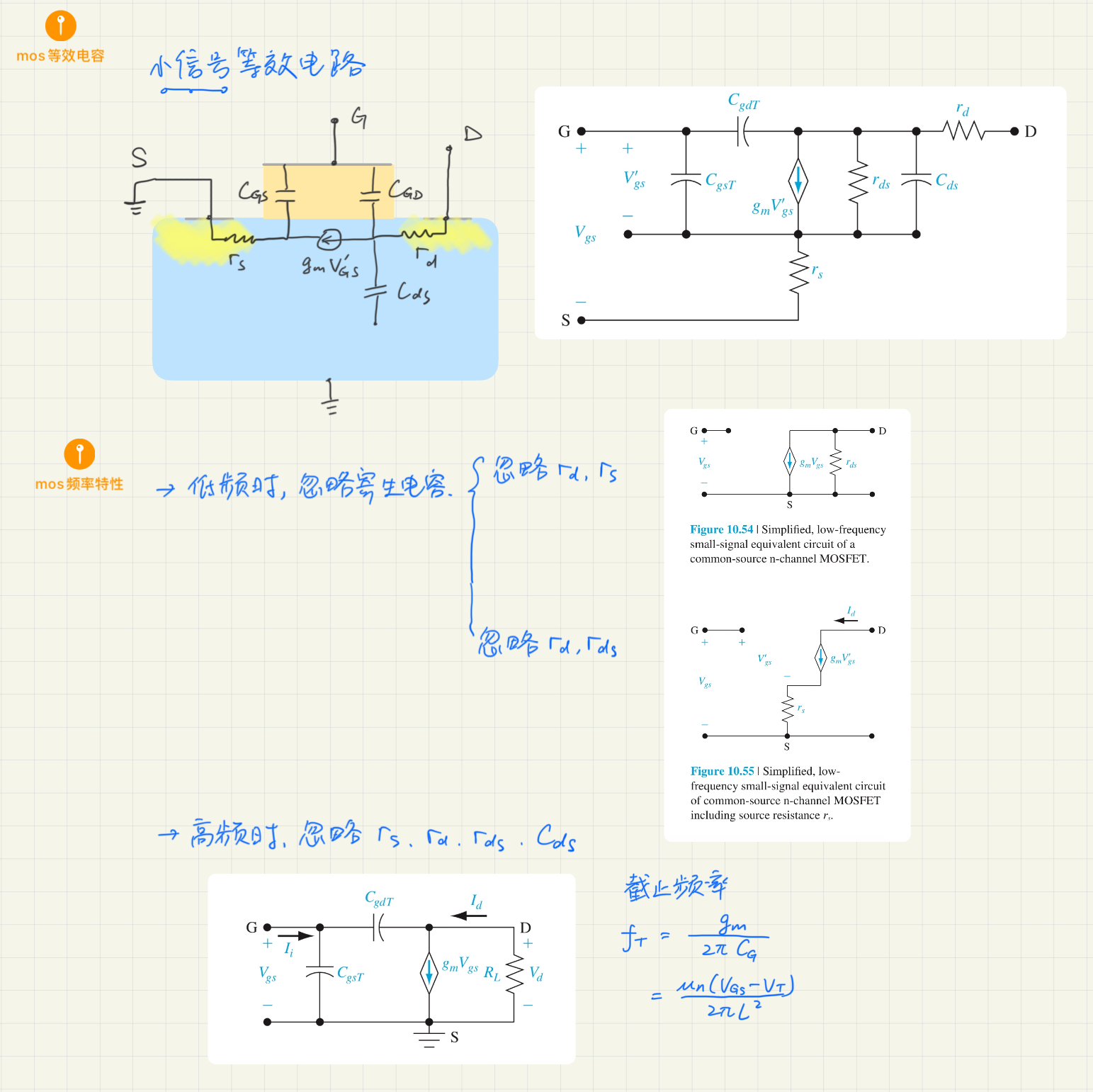

MOS的频率特性

频率限制的基本因素:

- 沟道输运时间。由于这个值一般较大,不影响MOS的典型频率响应。

- 栅电容充电时间。分析等效电容电路,在电流增益为1时认为到达截止频率。

问题:器件的截止频率与功率有什么关系?在施敏的书p211 5.4.1 中,提到功率-频率的乘积主要受材料参数的限制。由于雪崩击穿场强和载流子饱和速度的限制,典型的功率输出随 $1/f^2$ 变化。

具体推导有待进一步调查!

MOS的击穿

- 齐纳击穿,隧穿,主要出现在高掺杂的器件中。

- 雪崩击穿,主要击穿方式。

MOS器件的二阶效应

体效应:衬底和源极之间的电势差改变反型层厚度,导致 $V_{th}$ 发生变化。

考虑体效应之后,阈值电压变为:

体效应系数 $\gamma=\sqrt{2q\epsilon{sub}N{sub}}/C_{ox}$ ,可以通过调整电容和衬底掺杂来调整。

亚阈值导电性:当栅极电压小于阈值电压,存在弱反型层,源漏极之间存在电流。

沟道长度调制:若反型层长度 $L’$ 和 $V{DS}$ 无关,则在饱和区,一定栅压下漏极电流为常数。但实际中 $\Delta L /L = \lambda V{DS}$,即反型层长度的变化量与漏极电压成正比。$\lambda$ 为沟道调制系数。

则饱和区电流出现与 $V_{DS}$ 的线性关系:

饱和区跨导同样也会出现 $\lambda$ 的修正。

当沟道长度较短的时候,反型层长度变化的线性近似失效,饱和区电流不再呈线性变化。

载流子速度饱和:当沟道变短源漏电压变大,沟道电场变强,载流子会达到饱和速度。

对于Si,载流子饱和速度是 $10^7 cm/s$ ,在 $L=1\mu m,V_{DS}=5V$的情况下就会达到饱和速度。对于SiC,载流子饱和速度约是Si的二倍。

短沟道效应:源端和漏端的空间电荷区扩展到了沟道区域。

SiC CMOS 工艺

书:《碳化硅技术基本原理——生长、表征、器件和应用》第六章 碳化硅器件工艺

离子注入

由于SiC中的扩散系数比Si低很多,所以一般采用离子注入而不是扩散制造选择掺杂区。

典型掺杂区域:

| 区域 | 深度/um | 掺杂浓度/cm^-3 |

|---|---|---|

| source/drain | 0.2-0.3 | e19-e10 |

| p+ contact | 0.2-0.3 | e19-e20 |

| p well | 0.4-0.7 | e17-e18 |

箱式注入:采用多次不同剂量和不同能量注入,形成一定深度的近似均匀掺杂。

例如:400nm的箱式注入,总剂量为 110^14 cm^-2,对应的掺杂区域原子浓度为 210^18 cm^-3.

n型注入:注入氮和磷离子。

- 对于<0001>的晶面,需要采用7°的角度抑制沟道效应,最少应大于5°。

- 在高浓度注入(> e15cm^-2)时,应该采用高温注入(~500℃),否则就算高温退火也无法修复晶格损伤。

- 重掺杂n区域(>> e19cm^-3)应采用高温磷离子注入以进一步降低电阻。

- 退火温度应该高于1600℃。(典型退火:Ar气氛30min退火。)

p型注入:硼和铝离子。

- 硼因为具有异常的扩散,以及退火时会引起深层次缺陷,一般不采用。

- 更高温退火(~1750℃)可以得到更好的结特性,例如降低二极管漏电流。

- 高温注入重掺杂Al(~e19 cm^-3)的电阻率虽然相较于室温注入较低,但仍然比较大(~比n重掺杂区大100倍)。

高温退火时,利用碳膜可以有效提高表面平整度。

刻蚀

SiC的湿法刻蚀非常困难。一般采用反应离子刻蚀(RIE)。

相比于Si,SiC的刻蚀速率较低。

反应中可以加入氧气和氩气,增强碳原子的去除。

掩膜材料一般采用CVD淀积的二氧化硅。

热氧化

SiC的热氧化消耗量是46%。与Si接近。例如,生长100nm的氧化层需要消耗46nm的SiC。

热氧化之后的退火参数还需要进一步研究。

即使经过工艺优化,沟道迁移率还是会受到高密度表面态影响。

金属化

肖特基接触:没有重掺杂的情况下,大部分没有经过高温淀积在SiC上的金属,都是肖特基接触。

欧姆接触:由于SiC的禁带宽度较宽(3.26eV),在n型重掺杂区的欧姆接触需要金属功函数<4ev,在p型重掺杂区金属功函数需要 > 7 eV。

常用:n型 Ni ,p型 Al/Ti.

为了得到较低电阻率(< e-6 Omega*cm^2),需要高温烧结(950~1000℃)。

论文:CMOS Circuits on Silicon Carbide for High Temperature Operation

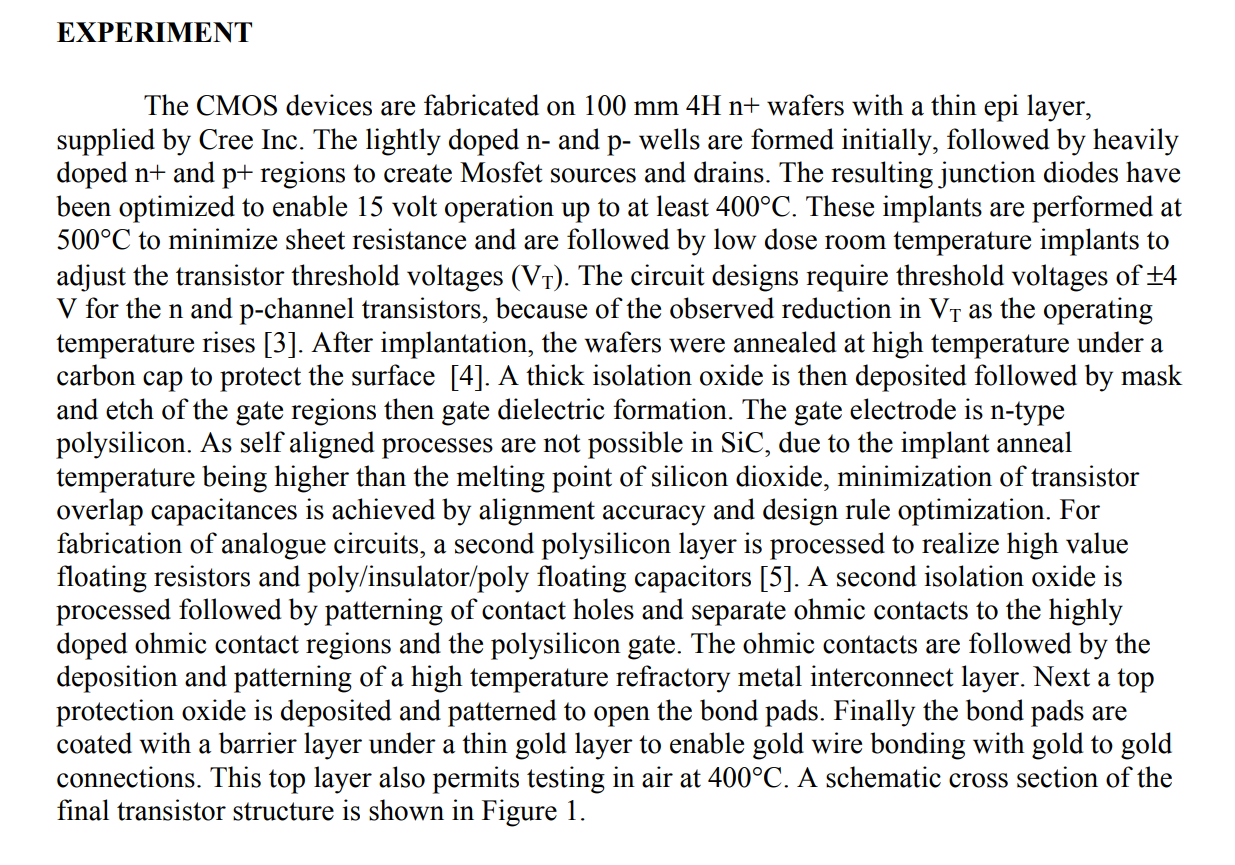

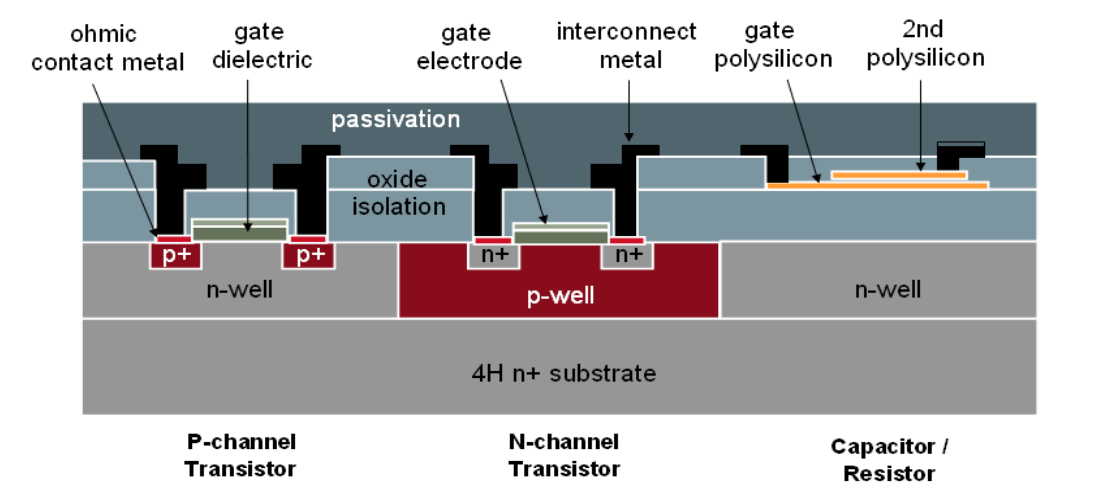

工艺要点:

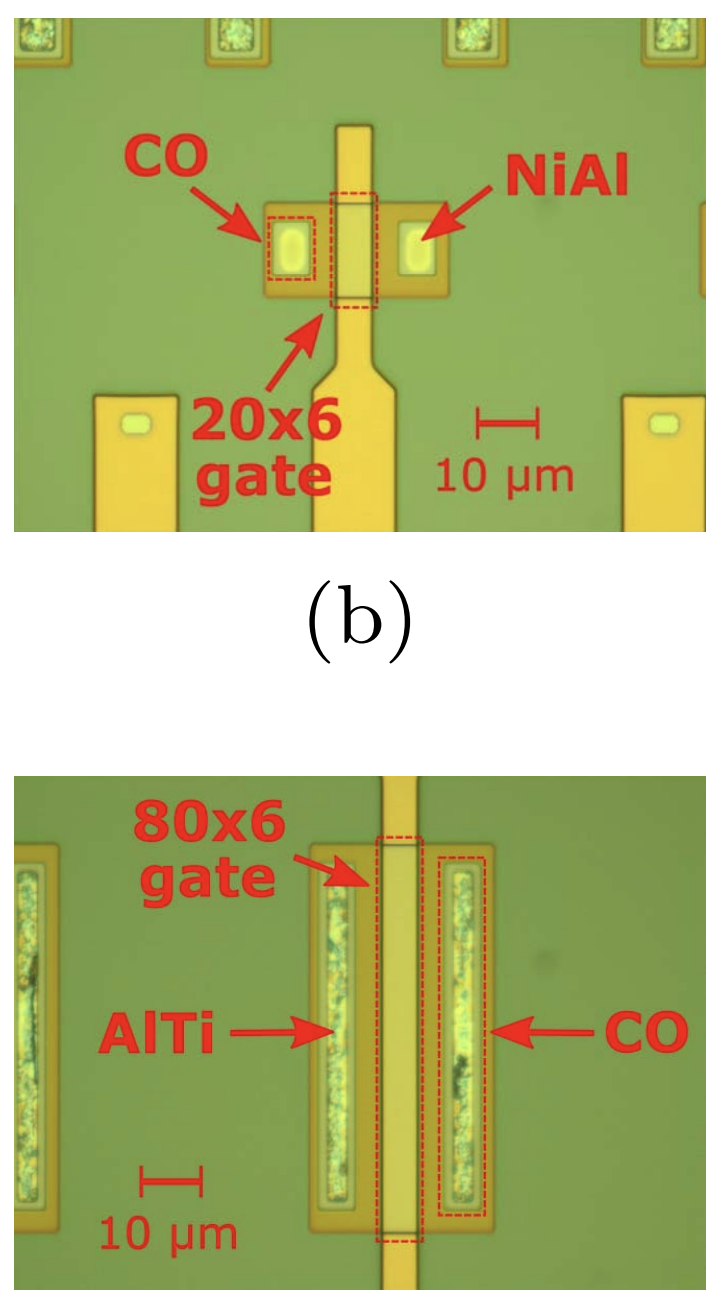

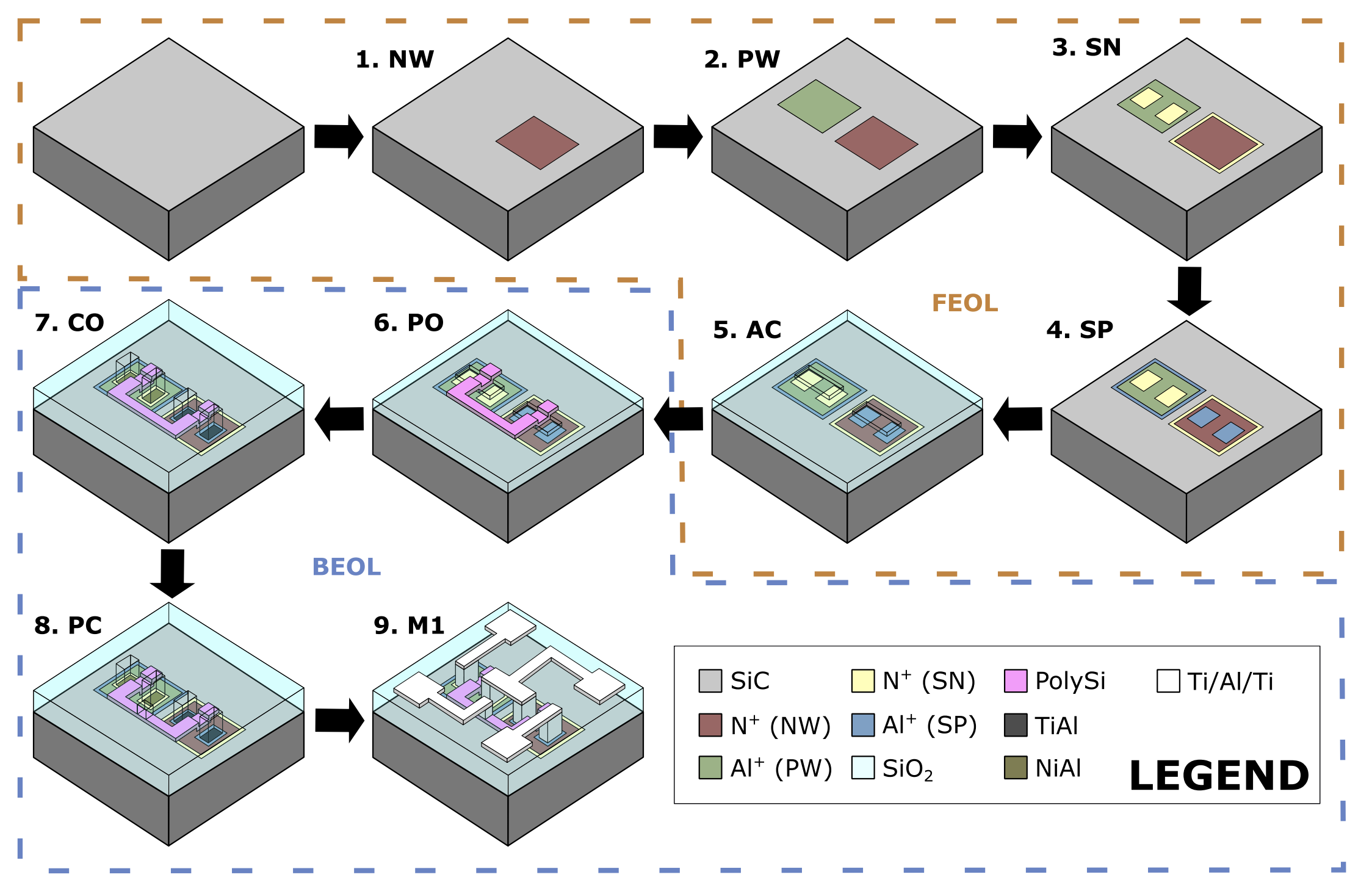

- 衬底是100mm 4H-SiC n+。

- 高温掺杂之后,进行室温的小剂量掺杂以调整阈值电压。

- 栅极电极是n掺杂的多晶硅。

- 为处理模拟信号,在旁边加入了一个电容。

论文:Scalable SiC CMOS Technology, 2022.

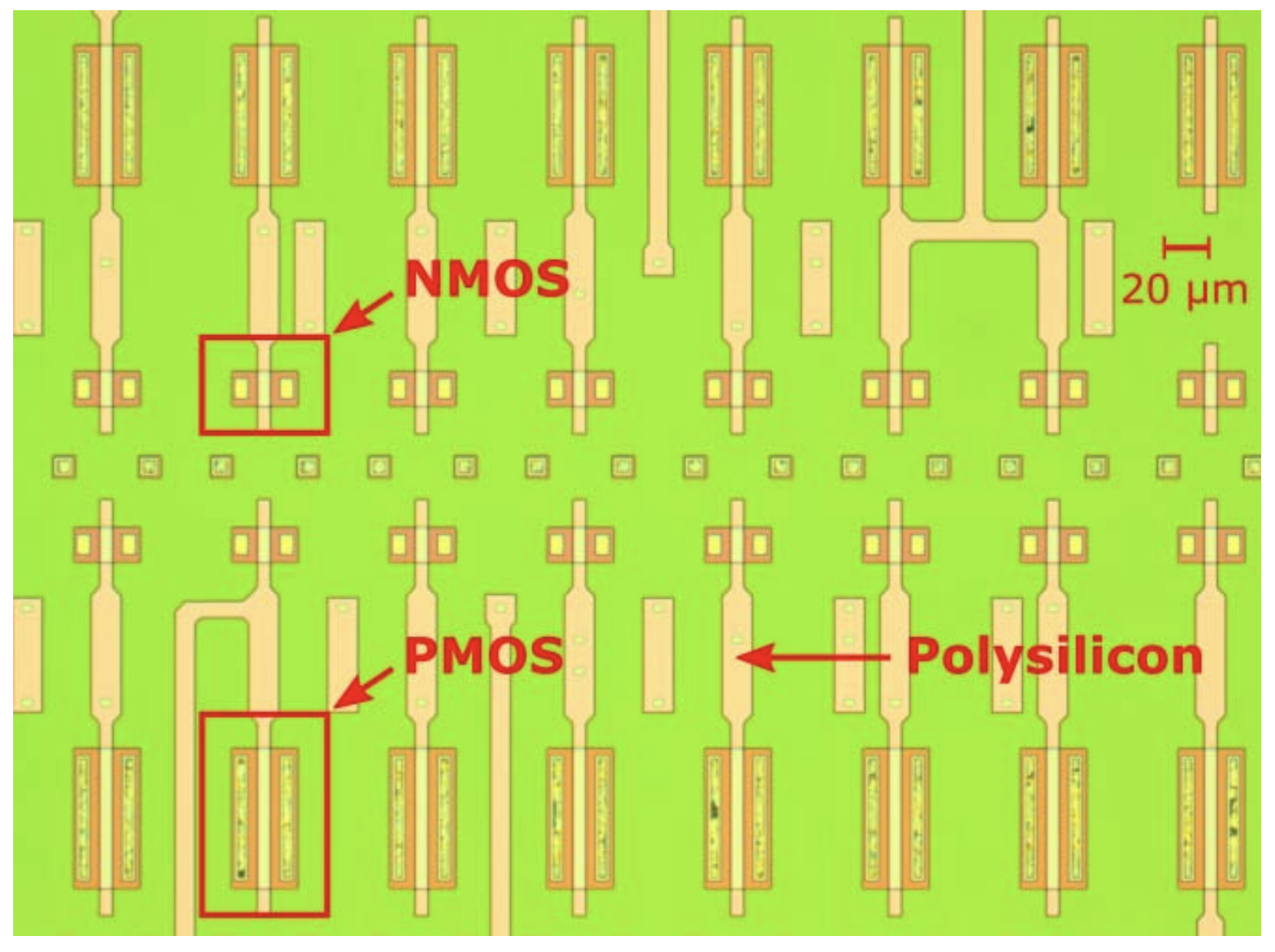

要点:为了实现CMOS中NMOS和PMOS的匹配,PMOS的尺寸(W)是NMOS的四倍。

(具体W/L的值可以通过计算得到,后续的笔记再整理这一部分)